Новость

Новое руководство: Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 2

10 сентября 2019 г.· FPGA-Systems archive· Руководство

В разделе по HLS появилось новое руководство: Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 2 В этой части будут описаны основные шаги для создания блок дизайна (работа в IP Integrator) для разработанных ранее IP-блоков...

В разделе по HLS появилось новое руководство: Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 2

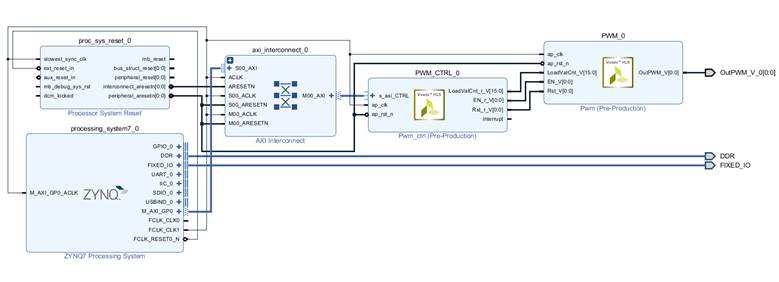

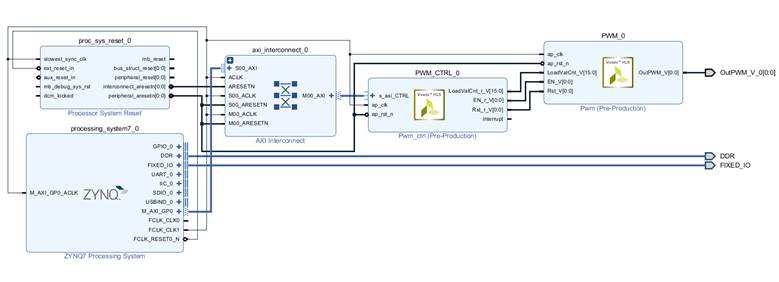

В этой части будут описаны основные шаги для создания блок дизайна (работа в IP Integrator) для разработанных ранее IP-блоков в среде Vivado HLS [1]. Интеграция будет производится для системы-на-кристалле ZYNQ-7000, а конкретно для Zynq установленного на плате MiniZed [2, 3].

ПервоисточникВ этой части будут описаны основные шаги для создания блок дизайна (работа в IP Integrator) для разработанных ранее IP-блоков в среде Vivado HLS [1]. Интеграция будет производится для системы-на-кристалле ZYNQ-7000, а конкретно для Zynq установленного на плате MiniZed [2, 3].