Новость

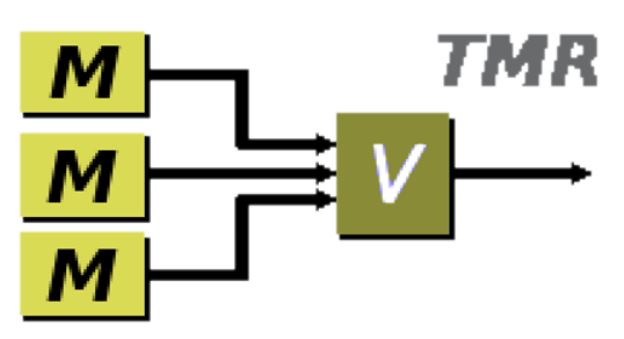

Реализация тройного модульного резервирования (TMR) на MicroBlaze

16 марта 2021 г.· FPGA-Systems archive· Заметка

Небольшое руководство о том, как разместить 3 софт-процессора MicroBlaze на отладочной плате Nexys 4 DDR FPGA (Xilinx Artix 7 FPGA) и затем реализовать тройное модульное резервирование для управления GPIO, используя IP-блок Triple Modular Redundancy (TMR) ...

Небольшое руководство о том, как разместить 3 софт-процессора MicroBlaze на отладочной плате Nexys 4 DDR FPGA (Xilinx Artix 7 FPGA) и затем реализовать тройное модульное резервирование для управления GPIO, используя IP-блок Triple Modular Redundancy (TMR)